Overview

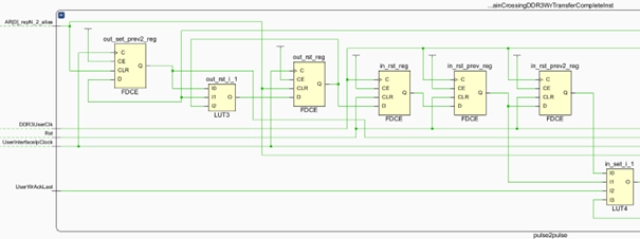

All products are delivered with a Board Support Package (BSP) containing a Register Transfer Level (RTL) reference design. The reference designs are coded in VHDL and demonstrate the capabilities of a product. For AMD based products, the default toolchains are Vivado and Vitis. The reference designs are build using generic IP blocks that can be imported as standard VHDL components or as Vivado IP integrator blocks. The IP blocks provide AXI4-Lite and AXI4-Streaming interfaces for register access and high-speed data transfers. This allows customers to connect their own proprietary IP directly to our standard IP blocks which accelerates the development.

Customers get a full BSP which includes software and RTL reference designs, programming files, executables and source code. Quick start guides help customers to get started quickly and accelerate their development.

Hybrid DSP also offers custom developments; from specific protocols and data processing IP, to fully automated, in-system test designs.

Reference designs are delivered with documentation and simulation test benches.

Features

Main Features

- Reference designs in VHDL

- Including testbench

- IP interconnect using standard AXI4 -Lite and AXI4-Streaming interfaces

- Generic IP library offering Vivado IP integrator components and standard VHDL components

- Supported host interfaces from FPGA (SoC PL)

- PCIe endpoint implementation with software API

- 10Gb Ethernet

- COM port/UART using a Hybrid DSP packet based protocol

- Front-end digital interfaces such as

- >1Gb LVDS with optimal eye link training including synchronization

- JESD204B/C

- VITA 17.3 sFPDP

- Aurora

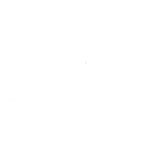

- Other IP blocks such as

- DDR4 FIFO

- AXI-Stream to AXI-Lite buffer

- 1000BASE-KX testing

- RS232, RS422 and RS485 controllers

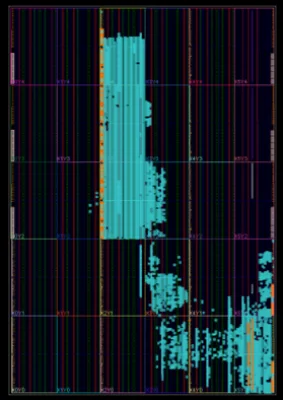

- Transceiver testing including in-system IBERT and link training

Deliverables

- Documentation with register map and description

- Vivado/Vitis project with source code and constraints

- Simulation testbench

- .bit and .mcs files

- Delivery methods such as a GIT customer facing repository or a .zip/.rar archive on (S)FTP or DVD